### **Features**

- Programmable DMUX Ratio:

- 1:4: Data Rate Max = 1 Gsps

- PD (8b/10b) < 4.3/4.7 W (ECL  $50\Omega$  output)

- 1:8: Data Rate Max = 2 Gsps

- PD (8b/10b) < 6/6.9 W (ECL  $50\Omega$  output)

- 1:16 with 1 TS8388B or 1 TS83102G0B and 2 DMUX

- Parallel Output Mode

- 8-/10-bit

- ECL Differential Input Data

- DataReady or DataReady/2 Input Clock

- Input Clock Sampling Delay Adjust

- Single-ended Output Data:

- Adjustable Common Mode and Swing

- Logic Threshold Reference Output

- (ECL, PECL, TTL)

- Asynchronous Reset

- Synchronous Reset

- ADC + DMUX Multi-channel Applications:

- Stand-alone Delay Adjust Cell for ADCs Sampling Instant Alignment

- Differential Data Ready Output

- Built-in Self Test (BIST)

- Dual Power Supply V<sub>EE</sub> = -5V, V<sub>CC</sub> = +5V

- Radiation Tolerance Oriented Design (More than 100 Krad (Si) Expected)

- TBGA 240 (Cavity Down) Package

## **Description**

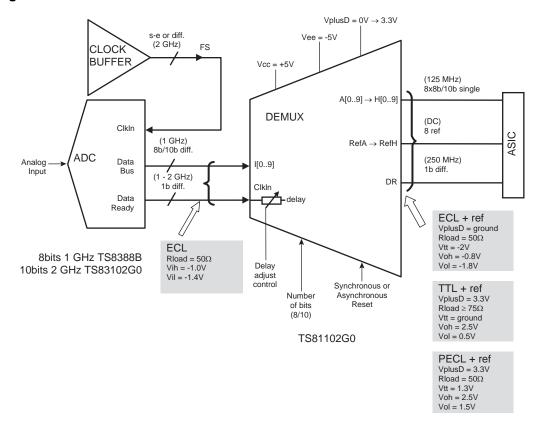

The TS81102G0 is a monolithic 10-bit high-speed (up to 2 GHz) demultiplexor, designed to run with all kinds of ADCs and more specifically with Atmel's high-speed ADC 8-bit 1 Gsps TS8388B and ADC 10-bit 2 Gsps TS83102G0B.

The TS81102G0 uses an innovative architecture, including a sampling delay adjust and tunable output levels. It allows users to process the high-speed output data stream down to processor speed and uses the very high-speed bipolar technology (25 GHz NPN cut-off frequency).

DMUX 8-/10-bit 2 GHz 1:4/8

TS81102G0

## **Block Diagram**

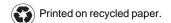

Figure 1. Block Diagram

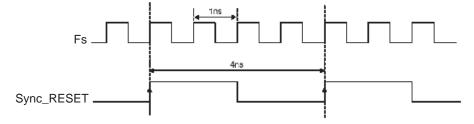

# Internal Timing Diagram

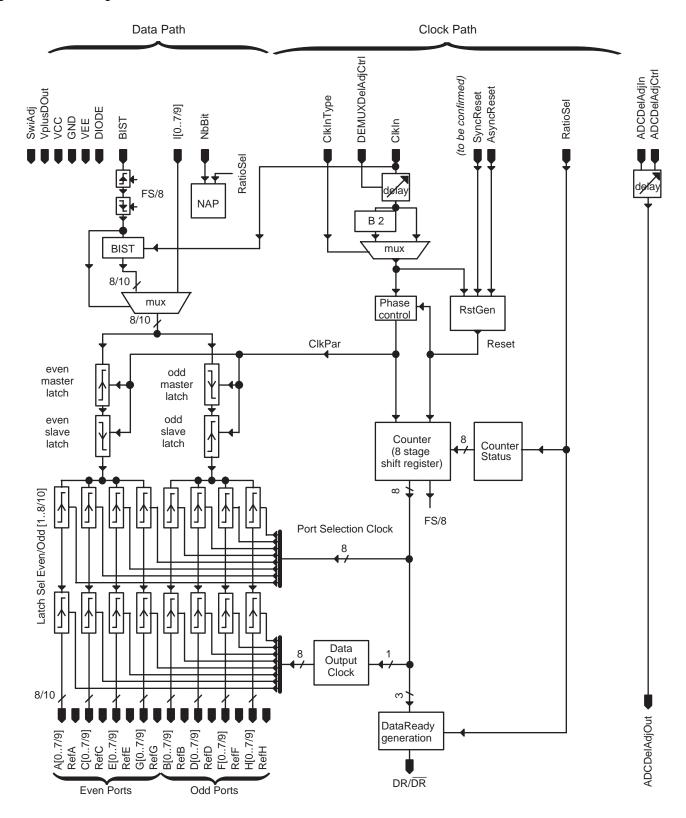

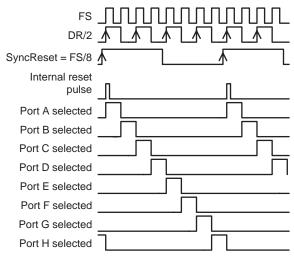

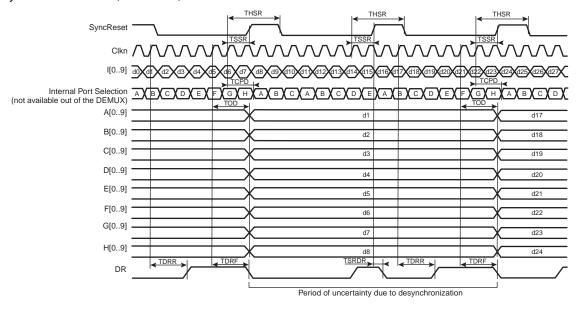

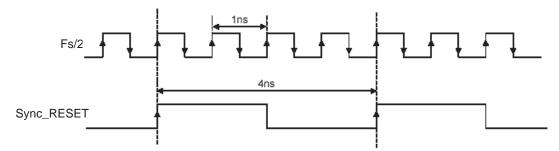

This diagram corresponds to an established operation of the DMUX with Synchronous Reset.

Figure 2. Internal Timing Diagram

# Functional Description

The TS81102G0 is a demultiplexer based on an advanced high-speed bipolar technology featuring a cutoff frequency of 25 GHz. Its role is to reduce the data rate so that the data can be processed at the DMUX output.

The TS81102G0 provides 2 programmable ratios: 1:4 and 1:8. The maximum data rate is 1 Gsps for the 1:4 ratio and 2 Gsps for the 1:8 ratio.

The TS81102G0 is able to process 8 or 10-bit data flows.

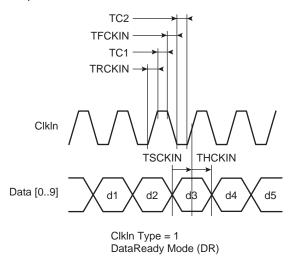

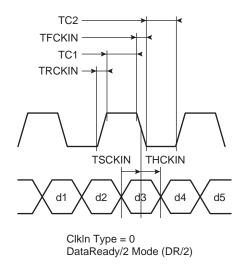

The input clock can be an ECL differential signal or single-ended DC coupled signal. Moreover it can be a DataReady or DataReady/2 clock.

The input digital data must be an ECL differential signal.

The output signals (Data Ready, digital data and reference voltage) are adjustable with VplusD independent power supply. Typical output modes are ECL, PECL or TTL.

The Data Ready output is a differential signal. The digital output data and reference voltages are single-ended signals.

The TS81102G0 is started by an Asynchronous Reset. A Synchronous Reset enables the user to re-synchronize the output port selection and to minimize loss of data that could occur within the DMUX.

A delay adjust cell is available to ensure a good phase between the DMUX' input clock and input data.

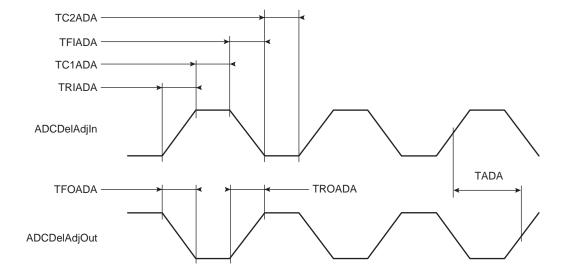

Another delay adjust cell is available to control the ADCss sampling instant alignment, in case of the ADCs interleaving.

A 10-bit generator is implemented in the TS81102G0, the Built-In Self Test (BIST). This test sequence is very useful for testing the DMUX at first use.

A fine tuning of the output swing is also available.

The TS81102G0 can be used with the following Atmel ADCs:

- TS8388B(F/FS/GL), 8-bit 1 Gsps ADC

- TS83102G0B, 10-bit 2 Gsps ADC

# Main Function Description

# Programmable DMUX Ratio

The conversion ratio is programmable: 1:4 or 1:8.

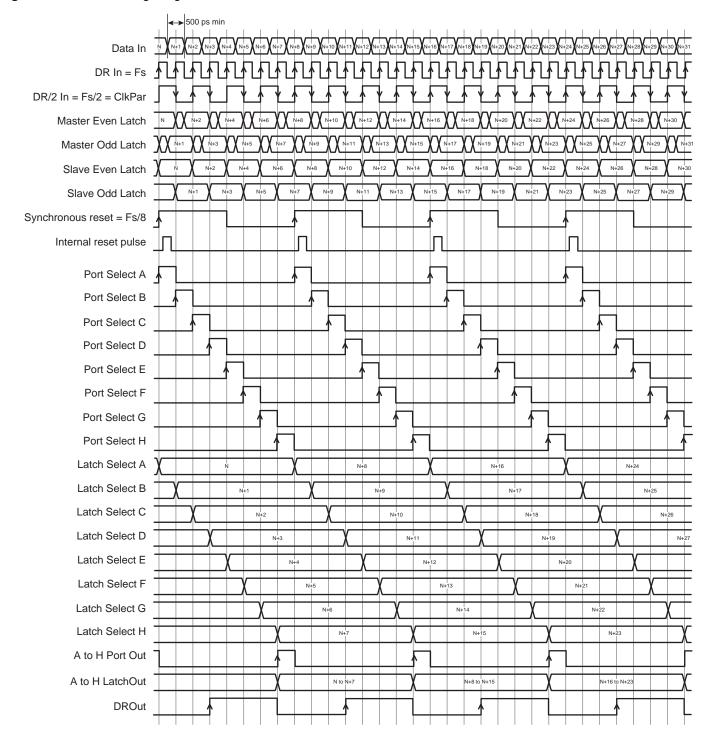

Figure 3. Programmable DMUX Ratio

# Parallel Output Mode

Figure 4. Parallel Mode

## Input Clock Sampling Delay Adjust (DEMUXDELADJCTRL)

The input clock phase can be adjusted with an adjustable delay (from 250 to 750 ps). This is to ensure a proper phase between the clock and input data of the DMUX.

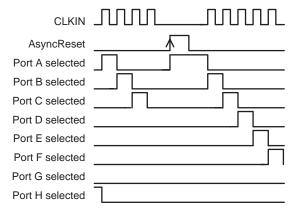

## Asynchronous Reset (ASYNCRESET)

Figure 5. Asynchronous Reset

The Asynchronous Reset is a master reset of the port selection, which works on TTL levels. It is active on the high level. During an asynchronous reset, the clock must be in a known state. It is used to start the DMUX.

When it is active, it paralyzes the outputs (the output clock and output data remain at the same level as before the asynchronous reset). When it comes back to its low level, the DMUX starts: the outputs are active and the first processed data is on port A.

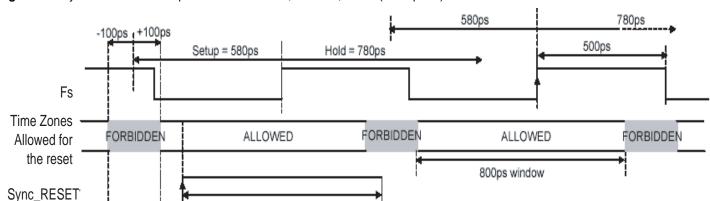

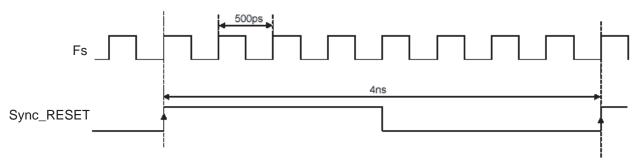

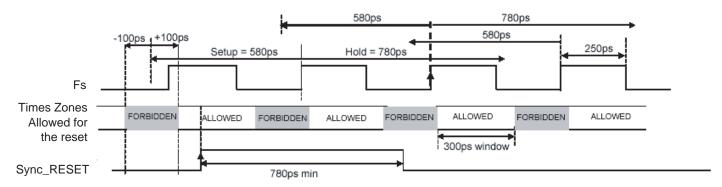

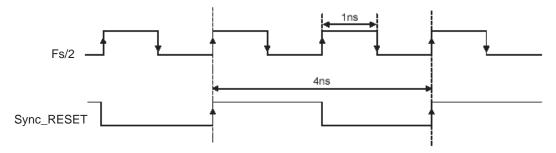

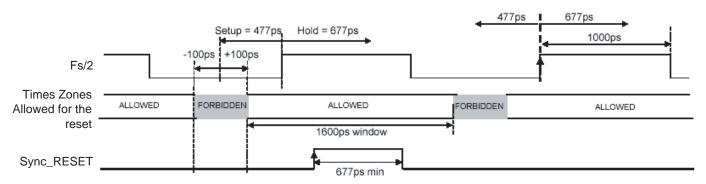

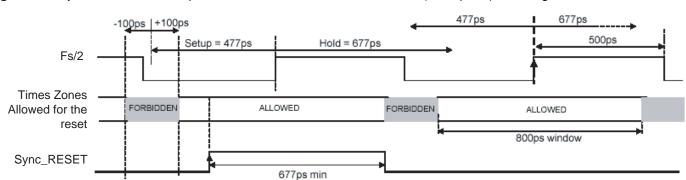

## Synchronous Reset (SYNCRESET)

Figure 6. Synchronous Reset

The DMUX can be synchronously reset to a programmable state depending on the conversion ratio. The clock must not be stopped during reset. The synchronization signal is a clock (SyncRest) whose frequency is FS/8\*n where n is an integer (n = 1,2,3,...) in 1:8 mode and FS/4\*n in 1:4 mode. The front edge of this clock is synchronized with Clkln inside the DMUX, and generates a 200 ps reset pulse. This reset pulse occurs during a fixed level of Clkln.

If the DMUX was synchronized with Syncreset previous to a possible loss of synchronization, then the output data is immediately correct, no modification can be seen at the output of the DMUX, and no data is lost ("Internal Timing Diagram" on page 3).

If the DMUX was not synchronized with SyncReset previous to a possible loss of synchronization, then the output data and data ready of the DMUX are changed. The output data is correct after a number of input clocks corresponding to the pipeline delay ("Timing Diagrams with Synchronous Reset" on page 19).

## Counter

# Programmable State

When the counter is reset, its initial states depends on the conversion ratio:

- 1:8: counting on 8 bits,

- 1:4: counting on 4 bits.

### **Pipeline Delay**

The maximum pipeline delay depends on the conversion ratio:

- 1:8: pipeline delay = 7

- 1:4: pipeline delay = 3

### 8-/10-bit, with NAP Mode for the 2 Unused Bit

The DMUX is a 10-bit parallel device. The last two bits (bits 8 and 9) may not be used, and the corresponding functions are set to nap mode to reduce power consumption.

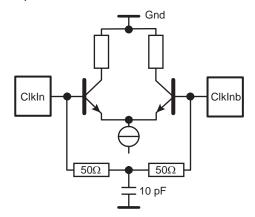

# ECL Differential Input Data

Input data are ECL compatible (Voh = -0.8V, Vol = -1.8V).

The minimum swing required is 100 mV differential.

All inputs have a  $100\Omega$  differential termination resistor. The middle point of these resistors is connected to ground through a 10 pF capacitor.

Figure 7. ECL Differential Input Data

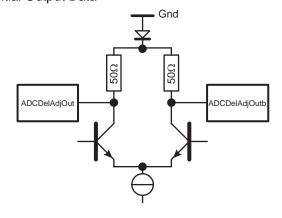

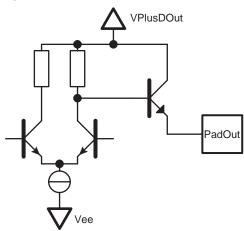

# **50** $\Omega$ Differential Output Data

The output clock for the ADC is generated through a  $50\Omega$  loaded long tailed. The  $50\Omega$  resistor is connected to the ground pad via a diode. The levels are (on the  $100\Omega$  differential termination resistor): Vol = -1.4V, Voh = -1.0V.

Figure 8.  $50\Omega$  Differential Output Data

### Single-ended Output Data

To reduce the pin number and power consumption of the DMUX, the eight output ports are single-ended.

To reach the high frequency output (up to 250 MHz) with a reasonable power consumption, the swing must be limited to a maximum of ±500 mV. The common mode is adjustable from -1.3V to +2V, with Vplus DOut pins. To ensure better noise immunity, a reference level (common mode) is available (one level by output port).

The output buffers are of ECL type (open emitters – not resistive adapted impedances). They are designed for a 15 mA average output current, and may be used with a  $50\Omega$  termination impedance.

Figure 9. Single-ended Output Data

Following are three application examples for these buffers: ECL/PECL/TTL. Please note that it is possible to have any other odd output format as far as current (36 mA max) and voltage (Vplus Dout –  $V_{EE} \leq 8.3$ V) limits are not overridden. The maximum frequency in TTL output mode depends on the load to be driven.

Table 1. Examples of Application of Buffers

| Parameter              | ECL  | PECL | TTL | Unit |

|------------------------|------|------|-----|------|

| VplusDout              | 0    | 3.3  | 3.3 | V    |

| Vtt                    | -2   | 1.3  | 0   | V    |

| Swing                  | ±0.5 | ±0.5 | ±1  | V    |

| Reference              | -1.3 | 2    | 1.5 | V    |

| Voh                    | -0.8 | 2.5  | 2.5 | V    |

| Vol                    | -1.8 | 1.5  | 0.5 | V    |

| Load                   | 50   | 50   | ≥75 | Ω    |

| Average Output Current | 14   | 14   | 15  | mA   |

| Output Data rate max.  | 250  | 250  | 250 | Msps |

This corresponds to the "Adjustable Logic Single" in the pinout description.

The "Adjustable Single" buffers for reference voltage are the same buffers, but the information available at the output of these buffers is more like analog than logic.

Note: The Max Output Data Rate is given for a typical  $50\Omega/2$  pF load.

# Differential Data Ready Output

The front edge of the DataReady output occurs when data is available on the corresponding port. The frequency of this clock depends on the conversion ratio (1:8 or 1:4), with a duty cycle of 50%.

The definition is the same as for single-ended output data, but the buffers are differential.

This corresponds to the "Adjustable Logic Differential" in the pinout description.

# Built-in Self Test (BIST)

A pseudo-random 10-bit generator is implemented in the DMUX. It generates a 10-bit signal in the output of the DMUX, with a period of 512 input clocks. The probability of occurrence of codes is uniformly spread over the 1024 possible codes: 0 or 1/1024.

Note that the 256 codes of bits 1 to 8 occur at least once. They start with a BIST command, in phase with the FS/8 clock on Port A. The logic output obtained on the A to H ports depends on the conversion ratio. The driving clock of BIST is Clkln. The ClklnType must be set to '1' (DataReady ADC clock) to have a different 10-bit code on each output.

The complete BIST sequence is available on request.

## **Specifications**

## Absolute Maximum Ratings

Table 2. Absolute Maximum Ratings

| Parameter                                                | Symbol                                                                                       | Comments                   | Value        | Unit |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------|--------------|------|

| Positive supply voltage                                  | V <sub>CC</sub>                                                                              |                            | GND to 6     | V    |

| Positive output buffer supply voltage                    | V <sub>PLUSD</sub>                                                                           |                            | GND to 4     | V    |

| Negative supply voltage                                  | V <sub>EE</sub>                                                                              |                            | GND to -6    | V    |

| Analog input voltages                                    | ADCDelAdjCtrl,<br>ADCDelAdjCtrlb or<br>DMUXDelAdjCtrl,                                       | Voltage range for each pad | -1 to +1     | V    |

|                                                          | DMUXDelAdjCtrlb or<br>SwiAdj                                                                 | Differential voltage range | -1 to +1     |      |

| ECL 50Ω input voltage                                    | ClkIn or ClkInb or I[09] or I[09]b or SyncReset or SyncResetb or ADCDelAdjin or ADCDelAdjinb | Voltage range for each pad | -2.2 to +0.6 | V    |

| Maximum difference between ECL $50\Omega$ input voltages | Clkln – Clklnb or<br>I[09] - I[09]b or<br>SyncReset –                                        | Minimum differential swing | 0.1          | V    |

|                                                          | Syncresetb or<br>ADCDelAdjln -<br>ADCDelAdjlnb                                               | Maximum differential swing | 2            |      |

Table 2. Absolute Maximum Ratings (Continued)

| Parameter                                                  | Symbol                                                | Comments        | Value                  | Unit |

|------------------------------------------------------------|-------------------------------------------------------|-----------------|------------------------|------|

| Data output current                                        | A[09] to H[09] or<br>RefA to RefH or<br>DR or DRb     | Maximum current | 36                     | mA   |

| TTL input voltage                                          | Clkln Type<br>RatioSel<br>NbBit<br>AsyncReset<br>BIST |                 | GND to V <sub>CC</sub> | V    |

| Maximum input voltage on diode for temperature measurement | DIODE                                                 |                 | 700                    | mV   |

| Maximum input current on diode                             | DIODE                                                 |                 | 8                      | mA   |

| Maximum junction temperature                               | T <sub>j</sub>                                        |                 | 135                    | °C   |

| Storage temperature                                        | T <sub>stg</sub>                                      |                 | -65 to 150             | °C   |

Note: Absolute maximum ratings are limiting values, to be applied individually, while other parameters are within specified operating conditions. Long exposure to maximum rating may affect device reliability. The use of a thermal heat sink is mandatory. See "Thermal and Moisture Characteristics" on page 26.

# Recommended Operating Conditions

Table 3. Recommended Operating Conditions

|                                       |                    |                                                | Reco  | mmended '                      | Value |      |

|---------------------------------------|--------------------|------------------------------------------------|-------|--------------------------------|-------|------|

| Parameter                             | Symbol             | Comments                                       | Min   | Тур                            | Max   | Unit |

| Positive supply voltage               | V <sub>CC</sub>    |                                                | 4.45  | 5                              | 5.25  | V    |

| Positive output buffer supply voltage | V <sub>PLUSD</sub> | ECL output compatibility                       | _     | 0                              | _     | V    |

| Positive output buffer supply voltage | V <sub>PLUSD</sub> | PECL output compatibility                      | _     | 3.3                            | _     | V    |

| Positive output buffer supply voltage | V <sub>PLUSD</sub> | TTL output compatibility                       | _     | 3.3                            | _     | V    |

| Negative supply voltage               | V <sub>EE</sub>    |                                                | -5.25 | -5                             | -4.75 | V    |

| Operating temperature range           | T <sub>J</sub>     | Commercial grade: "C"<br>Industrial grade: "V" |       | < Tc; Tj < 9<br>) < Tc; Tj < 1 |       | °C   |

Electrical

Operating

Characteristics

Tj (typical) =  $70^{\circ}$ C. Full Temperature Range:  $-40^{\circ}$ C < Tc; Tj <  $110^{\circ}$ C.

(Guaranteed temperature range are depending on part number)

Table 4. Electrical Specifications

|                                            |                    | Test  |       | Value |       |      |      |

|--------------------------------------------|--------------------|-------|-------|-------|-------|------|------|

| Parameter                                  | Symbol             | Level | Min   | Тур   | Max   | Unit | Note |

| Power Requirements                         |                    |       |       |       |       |      |      |

| Positive supply voltage                    |                    |       |       |       |       |      |      |

| V <sub>CC</sub>                            | $V_{CC}$           |       | 4.75  | 5     | 5.25  | V    |      |

| $V_{PLUSDOUT}$                             | _                  |       | _     | _     | _     | _    |      |

| ECL                                        | $V_{PLUSD}$        | 1     | -0.25 | 0     | 0.25  | V    |      |

| PECL                                       | $V_{PLUSD}$        |       | 3.135 | 3.3   | 3.465 | V    |      |

| TTL                                        | $V_{PLUSD}$        |       | 3.135 | 3.3   | 3.465 | V    |      |

| Negative supply voltage                    |                    |       |       |       |       |      |      |

| $V_{EE}$                                   | $V_{EE}$           | 1     | -5.25 | -5    | -4.75 | V    |      |

| Supply Currents                            |                    |       |       |       |       |      | (1)  |

| ECL (50 $\Omega$ ) and PECL (50 $\Omega$ ) |                    |       |       |       |       |      |      |

| V <sub>CC</sub> (for every configuration)  | $I_{CC}$           |       | _     | 31    | _     | mA   |      |

| 1:8, 8 bits                                | $I_{PLUSD}$        |       | 540   | 1180  | 1820  | mA   |      |

|                                            | I <sub>EE</sub>    |       | _     | 719   | _     | mA   |      |

| 1:8, 10 bits                               | $I_{PLUSD}$        |       | 640   | 1140  | 2240  | mA   |      |

|                                            | I <sub>EE</sub>    | 1     | _     | 790   | _     | mA   |      |

| 1:4, 8 bits                                | I <sub>PLUSD</sub> |       | 270   | 590   | 910   | mA   |      |

|                                            | I <sub>EE</sub>    |       | _     | 592   | _     | mA   |      |

| 1:4, 10 bits                               | I <sub>PLUSD</sub> |       | 320   | 720   | 1120  | mA   |      |

|                                            | I <sub>EE</sub>    |       | _     | 634   | _     | mA   |      |

| TTL (75Ω)                                  |                    |       |       |       |       |      |      |

| V <sub>CC</sub> (for every configuration)  | $I_{CC}$           |       | _     | 31    | _     | mA   |      |

| 1:8, 8 bits                                | I <sub>PLUSD</sub> |       | 760   | 1610  | 2440  | mA   |      |

|                                            | I <sub>EE</sub>    |       | _     | 872   | _     | mA   |      |

| 1:8, 10 bits                               | I <sub>PLUSD</sub> |       | 900   | 1770  | 3010  | mA   |      |

|                                            | I <sub>EE</sub>    | 1     | _     | 980   | _     | mA   |      |

| 1:4, 8 bits                                | I <sub>PLUSD</sub> |       | 380   | 810   | 1220  | mA   |      |

|                                            | I <sub>EE</sub>    |       | _     | 670   | _     | mA   |      |

| 1:4, 10 bits                               | I <sub>PLUSD</sub> |       | 450   | 880   | 1510  | mA   |      |

| ·                                          | I <sub>EE</sub>    |       | _     | 729   | _     | mA   |      |

| Nominal power dissipation                  |                    | 11.   | 1     | l     | 1     | II.  | (1)  |

| ECL (50Ω)                                  |                    |       |       |       |       |      |      |

| 1:8, 8 bits                                | PD                 |       | 5.2   | 5.6   | 6     | W    |      |

| 1:8, 10 bits                               | PD                 |       | 5.9   | 6.4   | 6.9   | W    |      |

| 1:4, 8 bits                                | PD                 | 1     | 3.9   | 4.1   | 4.3   | W    |      |

| 1:4, 10 bits                               | PD                 |       | 4.2   | 4.5   | 4.7   | W    |      |

Table 4. Electrical Specifications (Continued)

|                                                                                        |                                     | Test  |     | Value          |     |       |      |

|----------------------------------------------------------------------------------------|-------------------------------------|-------|-----|----------------|-----|-------|------|

| Parameter                                                                              | Symbol                              | Level | Min | Тур            | Max | Unit  | Note |

| PECL (50Ω)                                                                             |                                     |       |     |                |     |       |      |

| 1:8, 8 bits                                                                            | PD                                  |       | 5.8 | 6.2            | 6.6 | W     |      |

| 1:8, 10 bits                                                                           | PD                                  |       | 6.6 | 7.1            | 7.6 | W     |      |

| 1:4, 8 bits                                                                            | PD                                  | 1     | 4.2 | 4.4            | 4.6 | W     |      |

| 1:4, 10 bits                                                                           | PD                                  |       | 4.6 | 4.8            | 5.1 | W     |      |

| TTL (75Ω)                                                                              |                                     |       |     |                |     |       |      |

| 1:8, 8 bits                                                                            | PD                                  |       | 6.8 | 7.3            | 7.7 | W     |      |

| 1:8, 10 bits                                                                           | PD                                  |       | 7.8 | 8.4            | 9   | W     |      |

| 1:4, 8 bits                                                                            | PD                                  | 1     | 4.7 | 4.9            | 5.1 | W     |      |

| 1:4, 10 bits                                                                           | PD                                  |       | 5.2 | 5.5            | 5.8 | W     |      |

| Delay Adjust Control                                                                   |                                     |       |     |                |     |       |      |

| DMUXDelAdjCtrl differential voltage                                                    | DDAC                                |       | _   | _              | _   |       |      |

| 250 ps                                                                                 |                                     |       | _   | -0.5           | _   | V     |      |

| 500 ps                                                                                 |                                     | _     | _   | 0              | _   | V     |      |

| 750 ps                                                                                 |                                     |       | _   | 0.5            | _   | V     |      |

| Input current                                                                          | IDDAC                               |       | _   | _              | _   | mA    |      |

| ADCDelAdjCtrl differential voltage                                                     | ADAC                                |       | _   | _              | _   |       |      |

| 250 ps                                                                                 |                                     |       | _   | -0.5           | _   | V     |      |

| 500 ps                                                                                 |                                     | _     | _   | 0              | _   | V     |      |

| 750 ps                                                                                 |                                     |       | _   | 0.5            | _   | V     |      |

| Input current                                                                          | IADAC                               |       | _   | _              | _   | mA    |      |

| Digital Outputs                                                                        |                                     |       |     |                | I.  |       |      |

| ECL Output                                                                             |                                     |       |     |                |     |       |      |

| (assuming $V_{PLUSD} = 0V$ , SWIADJ = $0V$ , $50\Omega$ termination resistor on board) |                                     |       |     |                |     |       |      |

| Logic "0" voltage                                                                      | W                                   | 1     |     | -2.12          |     | V     |      |

| Logic "1" voltage                                                                      | V <sub>OL</sub>                     | '     | _   | -2.12<br>-1.16 | _   | V     |      |

| Reference voltage                                                                      | V <sub>OH</sub><br>V <sub>REF</sub> |       | _   | -1.16          | _   | V     |      |

| PECL Output                                                                            | ▼ REF                               |       |     | 1.40           |     | V     |      |

| (assuming $V_{PLUSD} = 3.3V$ , SWIADJ = 0V, $50\Omega$ termination resistor on board)  |                                     |       |     |                |     |       |      |

| Logic "0" voltage                                                                      |                                     | _     |     | 4.07           |     | 1.7   |      |

| Logic "1" voltage                                                                      | V <sub>OL</sub>                     | 1     | _   | 1.27           | _   | V     |      |

| Reference voltage                                                                      | V <sub>OH</sub>                     |       | _   | 2.44           | _   | V     |      |

|                                                                                        | V <sub>REF</sub>                    |       | 1   | 1.83           | _   | V     |      |

| TTL Output                                                                             |                                     |       |     |                |     |       |      |

| (assuming $V_{PLUSD}$ = 3.3V, SWIADJ = 0V, 75 $\Omega$ termination resistor on board)  |                                     |       |     |                |     |       |      |

| Logic "0" voltage                                                                      | $V_{OL}$                            | 1     | _   | 0.9            | _   | V     |      |

| Logic "1" voltage                                                                      | V <sub>OH</sub>                     |       | _   | 2.31           | _   | V     |      |

| Reference voltage                                                                      | V <sub>REF</sub>                    |       | _   | 1.2            | _   | V     |      |

| Output level drift with temperature (data and DR outputs)                              | _                                   | _     | _   | -1.3           | _   | mV/°C |      |

Table 4. Electrical Specifications (Continued)

|                                                         |                                    | Test  |           | Value  |           |        |      |

|---------------------------------------------------------|------------------------------------|-------|-----------|--------|-----------|--------|------|

| Parameter                                               | Symbol                             | Level | Min       | Тур    | Max       | Unit   | Note |

| Output level drift with temperature (reference outputs) | _                                  | 1     | _         | -0.9   | _         | mV/°C  |      |

| Digital Inputs                                          |                                    |       |           |        |           |        |      |

| ECL Input Voltages Logic "0" voltage Logic "1" voltage  | V <sub>IL</sub><br>V <sub>IH</sub> | 1     | -<br>-1.1 | _<br>_ | -1.4<br>- | V<br>V |      |

| TTL Input Voltages Logic "0" voltage Logic "1" voltage  | V <sub>IL</sub><br>V <sub>IH</sub> | 1     | -<br>2.0  | _<br>_ | 0.8       | V<br>V |      |

Note:

- 1. The supply current I<sub>PLUSD</sub> and the power dissipation depend on the state of the output buffers:

- the minimum values correspond to all the output buffers at low level,

- the maximum values correspond to all the output buffers at high level,

- the typical values correspond to an equal sharing-out of the output buffers between high and low levels.

Switching Performance and Characteristics

50% clock duty cycle (CLKIN, CLKINB). Tj (typical) = 70°C.

Full temperature range: -40°C < Tc; Tj < 110°C.

(Guaranteed temperature ranges depend on the part number)

See Timing Diagrams Figure 10 on page 16 to Figure 19 on page 21.

Table 5. Switching Performances

|                                       |                  | Test  |      | Value |     |      |      |

|---------------------------------------|------------------|-------|------|-------|-----|------|------|

| Parameter                             | Symbol           | Level | Min  | Тур   | Max | Unit | Note |

| Input Clock                           |                  |       |      |       |     |      |      |

| Maximum clock frequency               |                  |       |      |       |     |      |      |

| 1:8 ratio                             | FMAX             | _     | 2    | _     | 2.2 | GHz  |      |

| 1:4 ratio                             |                  |       | 1    | _     | 1.1 |      |      |

| Clock pulse width (high)              | TC1              | _     | 100  | _     | _   | ps   |      |

| Clock pulse width (low)               | TC2              | _     | 100  | _     | _   | ps   |      |

| Clock Path pipeline delay             |                  |       |      |       |     |      |      |

| DR input clock                        | TCPD             | _     | _    | 981   | _   | ps   | (1)  |

| DR/2 input clock                      | TCPD             |       | _    | 1084  | _   | ps   | (2)  |

| Clock rise/fall time                  | TRCKIN<br>TFCKIN | _     | _    | 100   | _   | ps   |      |

| Asynchronous Reset                    |                  |       |      |       |     |      |      |

| Asynchronous Reset pulse width        | PWAR             | _     | 1000 | _     | _   | ps   |      |

| Setup time from Asynchronous to ClkIn | TSAR             | _     | _    | 1500  | _   | ps   |      |

| Rise/fall time for (10% – 90%)        | TRAR<br>TFAR     | _     | 1000 | _     | _   | ps   |      |

Table 5. Switching Performances (Continued)

|                                                                                                                                 |           | Test  |             | Value                |                  |                             |              |

|---------------------------------------------------------------------------------------------------------------------------------|-----------|-------|-------------|----------------------|------------------|-----------------------------|--------------|

| Parameter                                                                                                                       | Symbol    | Level | Min         | Тур                  | Max              | Unit                        | Note         |

| Synchronous Reset                                                                                                               | <u>.</u>  |       |             |                      |                  |                             |              |

| Setup time from SyncReset to Clkln<br>DR input clock<br>DR/2 input clock                                                        | TSSR      | _     | _<br>_      | -580<br>-477         | _<br>_           | ps<br>ps                    | (3)<br>(4)   |

| Hold time from ClkIn to SyncReset<br>DR input clock<br>DR/2 input clock                                                         | THSR      | -     | _<br>_      | 780<br>677           | -<br>-           | ps<br>ps                    | (5)<br>(6)   |

| Rise/fall for (10% – 90%)                                                                                                       | TSRR/TFSR | _     | 100         | _                    | _                | ps                          |              |

| Input Data                                                                                                                      |           |       |             |                      |                  |                             |              |

| Setup time from I[09] to ClkIn DR input clock DR/2 input clock                                                                  | TSCKIN    | -     | <u>-</u>    | -794<br>-691         | -<br>-           | ps<br>ps                    | (7)<br>(8)   |

| Hold time from ClkIn to I[09] DR input clock DR/2 input clock                                                                   | THCKIN    | _     | _<br>_      | 994<br>891           | -<br>-           | ps<br>ps                    | (9)<br>(10)  |

| Rise/fall for (10% – 90%)                                                                                                       | TRDI/TFDI | _     | 100         | _                    | _                | ps                          |              |

| Output Data                                                                                                                     |           |       |             |                      |                  |                             |              |

| Data output delay DR input clock DR/2 input clock                                                                               | TOD       | _     | _<br>_      | 1820<br>1717         | <b>-</b>         | ps<br>ps                    | (11)<br>(12) |

| Data pipeline delay DR input clock, 1:4 ratio DR input clock, 1:8 ratio DR/2 input clock, 1:4 ratio DR/2 input clock, 1:8 ratio | TPD       | -     | -<br>-<br>- | 3<br>7<br>3/2<br>7/2 | -<br>-<br>-<br>- | Number<br>of input<br>clock | (13)         |

| Rise/fall for (10% – 90%)                                                                                                       | TROD/tfod | _     | _           | 497/484              | _                | ps                          | (14)         |

| Data Ready                                                                                                                      | 1         |       | I.          |                      |                  |                             |              |

| Data ready Falling edge<br>DR input clock<br>DR/2 input clock                                                                   | TDRF      | _     | -<br>-      | 1856<br>1753         | <b>-</b>         | ps<br>ps                    | (15)<br>(16) |

| Data ready Rising edge DR input clock DR/2 input clock                                                                          | TDRR      | _     | -<br>-      | 1828<br>1725         | <u>-</u>         | ps<br>ps                    | (17)<br>(18) |

| Asynchr; Reset to DataReady delay                                                                                               | TARDR     | _     | _           | 1918                 | _                | ps                          | (19)         |

| Synchr. Reset to DataReady delay                                                                                                | TSRDR     | _     | _           | 1037                 | _                | ps                          | (20)         |

| Rise/fall for (10% – 90%)                                                                                                       | TRDR/TFDR | _     | _           | 450                  | _                | ps                          | (21)         |

| Rising edge uncertainty                                                                                                         | JITTER    | _     | _           | 62                   | _                | ps                          |              |

| Built-In Self Test                                                                                                              |           |       |             | -                    |                  | •                           |              |

| Hold time from ClkIn to BIST                                                                                                    | THBIST    | _     | _           | _                    | _                | ps                          | (22)         |

Table 5. Switching Performances (Continued)

|                                                  |                   | Test  |            | Value      |        |       |              |

|--------------------------------------------------|-------------------|-------|------------|------------|--------|-------|--------------|

| Parameter                                        | Symbol            | Level | Min        | Тур        | Max    | Unit  | Note         |

| Setup time from Bist to ClkIn                    | TSBIST            | _     | _          | 1000       | _      | ps    |              |

| Rise/fall time for (10% – 90%)                   | TRBIST/<br>TFBIST | _     | 1000       | _          | _      | ps    |              |

| ADC Delay Adjust                                 | <u> </u>          | +     |            |            |        |       |              |

| Input frequency                                  | FMADA             | _     | 2          | _          | 2.2    | GHz   |              |

| Input pulse width (high)                         | TC1ADA            | _     | 90         | _          | _      | ps    |              |

| Input pulse width (low)                          | TC2ADA            | _     | 90         | _          | _      | ps    |              |

| Input rise/fall time                             | TRIADA/<br>TFIADA | _     | 100<br>100 | 150<br>150 | _<br>_ | ps    |              |

| Output rise/fall time                            | TROADA/<br>TFOADA | _     | _<br>_     | 145<br>104 | _<br>_ | ps    | (23)         |

| Data output delay (typical delay adjust setting) | TADA              | -     | _<br>_     | 784<br>896 | _<br>_ | ps    | (24)<br>(25) |

| Output delay drift with temperature              | TADAT             | _     | _          | 2.5        | _      | ps/°C |              |

| Output delay uncertainly                         | JITADA            | _     | _          | 30         | _      | ps    |              |

Notes: 1. TCPD is tuned with DMUXDelAdjCtrl: TCPD = 981 ± 250 ps.

- 2. TCPD is tuned with DMUXDelAdjCtrl: TCPD =  $1084 \pm 250$  ps.

- 3. TSSR depends on DMUXDelAdjCtrl: TSSR = -580 ± 250 ps. TSSR < 0 because of Clock Path internal delay.

- 4. TSSR depends on DMUXDelAdjCtrl: TSSR = -477 ± 250 ps. TSSR < 0 because of Clock Path internal delay.

- 5. THSR depends on DMUXDelAdjCtrl: THSR =  $780 \pm 250$  ps.

- 6. THSR depends on DMUXDelAdjCtrl: THSR = 677 ± 250 ps.

- 7. TSCKIN depends on DMUXDelAdjCtrl: TSCKIN = -794 ± 250 ps. TSCKIN < 0 because of Clock Path internal delay.

- 8. TSCKIN depends on DMUXDelAdjCtrl: TSCKIN = -691 ± 250 ps. TSCKIN < 0 because of Clock Path internal delay.

- 9. THCKIN depends on DMUXDelAdjCtrl: THCKIN =  $994 \pm 250$  ps.

- 10. THCKIN depends on DMUXDelAdjCtrl: THCKIN = 891 ± 250 ps.

- 11. TOD depends on DMUXDelAdjCtrl: TOD = 1820  $\pm$  250 ps. TOD is given for ECL 50 $\Omega$ /2 pFoutput load.

- 12. TOD depends on DMUXDelAdjCtrl: TOD = 1717  $\pm$  250 ps. TOD is given for ECL 50 $\Omega$ /2 pFoutput load.

- 13. TPD is the number of Clkln clock cycle from selection of Port A to selection of Port H in 1:8 conversion mode, and from selection of Port A to selection of Port D in 1:4 conversion mode. It is the maximum number of Clkln clock cycle, or pipeline delay, that a data has to stay in the DMUX before being sorted out. This maximum delay occurs for the data sent to Port A. For instance, the data sent to Port H goes directly from the input to the Port H, and its pipeline is 0. But even for this data, there is an additional delay due to physical propagation time in the DMUX.

- 14. TROD and TFOD are given for ECL  $50\Omega/2$  pF output load. In TTL mode, the TROD and TFOD are twice the ones for ECL. (For other termination topology, apply proper derating value 50 ps/pF in ECL, 100 ps/pF in TTL mode.)

- 15. TDRF depends on DMUXDelAdjCtrl: TDRF = 1856  $\pm$  250 ps. It is given for ECL 50 $\Omega$ /2 pF output load.

- 16. TDRF depends on DMUXDelAdjCtrl: TDRF = 1753  $\pm$  250 ps. It is given for ECL 50 $\Omega$ /2 pF output load.

- 17. TDRR depends on DMUXDelAdjCtrl: TDRR = 1858  $\pm$  250 ps. It is given for ECL 50 $\Omega$ /2 pF output load.

- 18. TDRR depends on DMUXDelAdjCtrl: TDRR = 1725  $\pm$  250 ps. It is given for ECL 50 $\Omega$ /2 pF output load.

- 19. TARDR is given for ECL  $50\Omega/2$  pF output load.

- 20. TSRDR is given for ECL  $50\Omega/2$  pF output load. It is minimum value since RstSync clock is synchronized with Clkln clock.

- 21. TRDR and TFDR are given for ECL  $50\Omega/2$  pF output load.

- 22. THBIST depends on the configuration of the DMUX. There must be enough Clkln clock cycles to have all the 512 codes, (see different Timing Diagrams).

- 23. With transmission line (ZO =  $50\Omega$ ) and output load R =  $50\Omega$ ; C = 2 pF.

- 24. Without output load.

- 25. With transmission line (ZO =  $50\Omega$ ) and output load R =  $50\Omega$ ; C = 2 pF.

### **Input Clock Timings**

Figure 10. Input Clock

# ADC Delay Adjust Timing Diagram

Figure 11. ADC Delay Adjust Timing Diagram

### Timing Diagrams with Asynchronous Reset

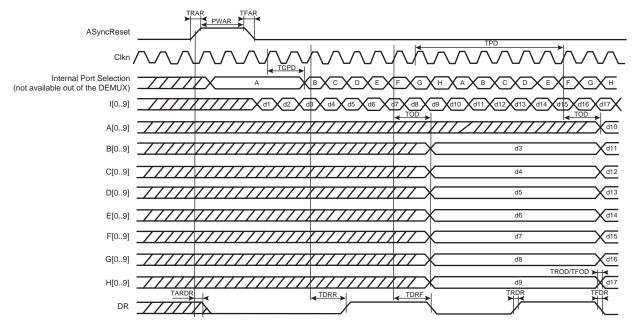

With a nominal tuning of DMUXDelAdj at a frequency of 2 GHz, d1 and d2 data is lost because of the internal clock's path propagation delay TCPD. TCPD is tuned with DMUXDelAdjCtrl pins to obtain good setup and hold times between Clkln and the data.

Figure 12. Start with Asynchronous Rest, 1:8 Ratio, DR Mode

With a nominal tuning of DMUXDelAdj at 2 GHz, d1 and d2 data is lost because of the internal clock's path propagation delay TCPD. TCPD is tuned with DMUXDelAdjCtrl pins to obtain good setup and hold times between Clkln and the input data. This timing diagram does not change with the opposite phase of Clkln.

Figure 13. Start with Asynchronous Rest, 1:8 Ratio, DR/2 Mode

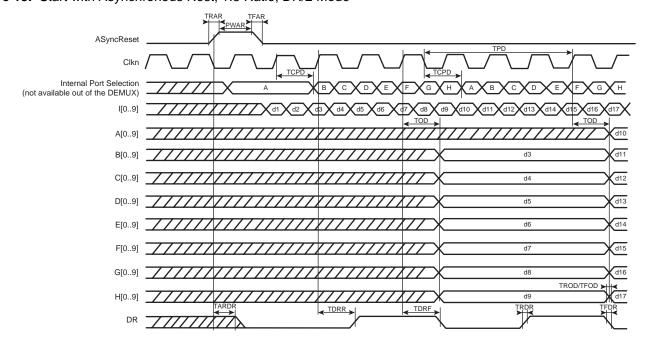

With a nominal tuning of DMUXDelAdj, at 1 GHz (1:4 mode) d1 data is lost because of the internal clock's path propagation delay TCPD. TCPD is tuned with DMUXDelAdjCtrl pins and is used to obtain good setup and hold times between Clkln and the input data.

Figure 14. Start with Asynchronous Reset, 1:4 Ratio, DR Mode

With a nominal tuning of DMUXDelAdj, at 1 GHz (1:4 mode) d1 data is lost because of the internal clock's path propagation delay TCPD. TCPD is tuned with DMUXDelAdjCtrl pins and is used to obtain good setup and hold times between Clkln and the input data. This timing diagram does not change with the opposite phase of Clkln.

Figure 15. Start with Asynchronous Reset, 1:4 Ratio, DR/2 Mode

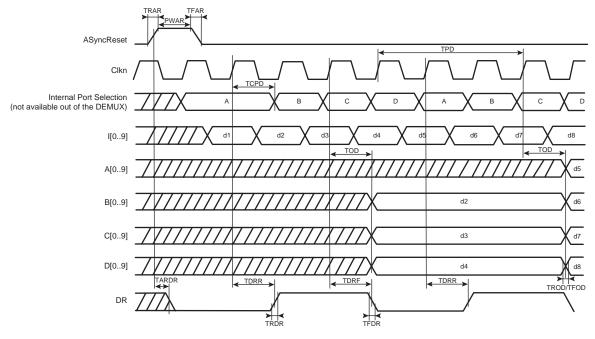

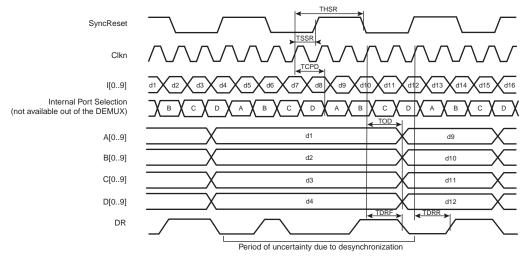

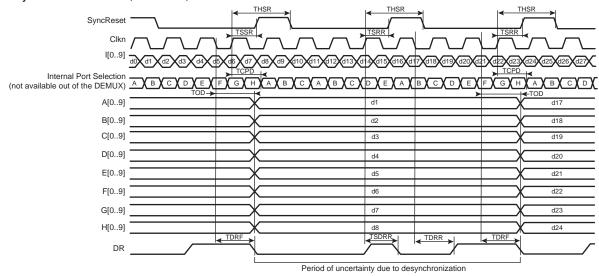

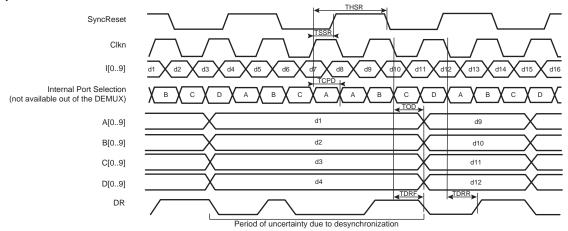

## Timing Diagrams with Synchronous Reset

Following is an example of the Synchronous Reset's utility in case of de-synchronization of the DMUX output port selection. The de-synchronization event happens after the selection of Port D.

DMUXDelAdjCtrl value is nominal. TSSR < 0 because of Clkln's internal propagation delay TCPD. After selection of Port C, instead of selecting Port D, the de-synchronization makes the port selection to restart on Port A. Since Port H was not selected, the data is not output to the ports but the last data (d1 to d8) is latched until the next selection of Port H. d9 to d16 are lost. The synchronous Reset ensures a re-synchronization of the port selection.

Figure 16. Synchronous Reset, 1:8 Ratio, DR Mode

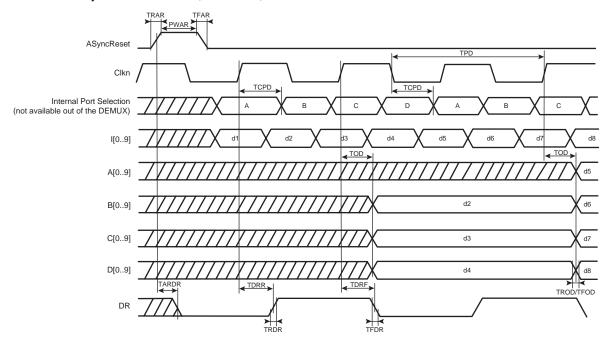

Example of the Synchronous Reset's utility in case of de-synchronization of the DMUX output port selection. The de-synchronization event happens after the selection of Port D.

DMUXDelAdjCtrl value is nominal. TSSR < 0 because of Clkln's internal propagation delay TCPD. After selection of Port C, instead of selecting Port D, the de-synchronization makes the port selection to restart on Port A. Since Port H was not selected, the data is not output to the ports but the last data (d1 to d4) is latched until the next selection of Port H. d5 to d8 are lost. The synchronous Reset ensures a re-synchronization of the port selection.

Figure 17. Synchronous Reset, 1:4 Ratio, DR Mode

Example of Synchronous Reset's utility in case of de-synchronization of the DMUX output port selection. The de-synchronization event happens after the selection of Port D.

DMUXDelAdjCtrl value is nominal. TSSR < 0 because of Clkln's internal propagation delay TCPD. After selection of Port C, instead of selecting Port D, the de-synchronization makes the port selection to restart on Port A. Since Port H was not selected, the data is not output to the ports but the last data (d1 to d8) is latched until the next selection of Port H. d9 to d16 are lost. The synchronous Reset ensures a re-synchronization of the port selection.

Figure 18. Synchronous Reset, 1:8 ratio, DR/2 Mode

Example of Synchronous Reset's utility in case of de-synchronization of the DMUX output port selection. The de-synchronization event happens after the selection of Port D.

DMUXDelAdjCtrl value is nominal. TSSR < 0 because of Clkln's internal propagation delay TCPD. After selection of Port C, instead of selecting Port D, the de-synchronization makes the port selection to restart on Port A. Since Port H was not selected, the data is not output to the ports but the last data (d1 to d4) is latched until the next selection of Port H. d5 to d8 are lost. The synchronous Reset ensures a re-synchronization of the port selection.

Figure 19. Synchronous Reset, 1:4 ratio, DR/2 Mode

Note: In case of low clock frequency and start with asynchronous reset, only the first data is lost and the first data to be processed is the second one. This data is output from the DMUX through port B.

## **Explanation of Test Levels**

Table 6. Explanation of Test Levels

| Num | Characteristics                                                                                                            |

|-----|----------------------------------------------------------------------------------------------------------------------------|

| 1   | 100% production tested at +25°C. <sup>(1)</sup>                                                                            |

| 2   | 100% production tested at +25°C, and sample tested at specified temperatures. (1)                                          |

| 3   | Sample tested only at specified temperatures.                                                                              |

| 4   | Parameter is guaranteed by design and characterization testing (thermal steady-state conditions at specified temperature). |

| 5   | Parameter is a typical value only.                                                                                         |

- Notes: 1. The level 1 and 2 tests are performed at 50 MHz.

- 2. Only MIN and MAX values are guaranteed (typical values are issuing from characterization results).

## **Package Description**

## **Pin Description**

Table 7. TS81102G0 Pin Description

| Туре            | Name                      | Levels                                                   | Comments                                                                                                                                                                            |

|-----------------|---------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Digital Inputs  | I[09]                     | Differential ECL                                         | Data input. On-chip $100\Omega$ differential termination resistor.                                                                                                                  |

|                 | ClkIn                     | Differential ECL                                         | Clock input (Data Ready ADC). On-chip $100\Omega$ differential termination resistor.                                                                                                |

| Outputs         | $A[09] \rightarrow H[09]$ | Adjustable Logic<br>Single                               | Data ready for port A to H. Common mode is adjusted with VplusDOut. Swing is adjusted with SwiAdj. $50\Omega$ termination possible.                                                 |

|                 | DR                        | Adjustable Logic<br>Differential                         | Data ready for channel A to H. Common mode is adjusted with VplusDOut. Swing is adjusted with SwiAdj. $50\Omega$ termination possible.                                              |

|                 | RefA → RefH               | Adjustable Single                                        | Reference voltage for output channels A to H. Common mode is adjustable with VplusDOut. $50\Omega$ termination possible.                                                            |

| Control Signals | ClkInType                 | TTL                                                      | DataReady or Dataready/2: logic 1: Data Ready.                                                                                                                                      |

|                 | RatioSel                  | TTL                                                      | DMUX ratio; logic 1: 1:4                                                                                                                                                            |

|                 | Bist                      | TTL                                                      | Reset and Switch of built-in Self Test (BIST): logic 0: BIST active.                                                                                                                |

|                 | SwiAdj                    | 0V ± 0.5V                                                | Swing fine adjustment of output buffers.                                                                                                                                            |

|                 | Diode                     | Analog                                                   | Diode for chip temperature measurement.                                                                                                                                             |

|                 | NbBit                     | TTL                                                      | Number of bit 8 or 10: logic 1: 10-bit.                                                                                                                                             |

| Synchronization | AsyncReset                | TTL                                                      | Asynchronous reset: logic 1: reset on.                                                                                                                                              |

|                 | SyncReset                 | Differential ECL                                         | Synchronous reset: active on rising edge.                                                                                                                                           |

|                 | DMUXDelAdjCtrl            | Differential analog input of ±0.5V around 0V common mode | Control of the delay line of DataReady input:<br>differential input = -0.5V: delay = 250 ps<br>differential input = 0V: delay = 500 ps<br>differential input = 0.5V: delay = 750 ps |

|                 | ADCDelAdjCtrl             | Differential analog input of ±0.5V around 0V common mode | Control of the delay line for ADC:<br>differential input = - 0.5V: delay = 250 ps<br>differential input = 0V: delay = 500 ps<br>differential input = 0.5V: delay = 750 ps           |

|                 | ADCDelAdjIn               | Differential ECL                                         | Stand-alone delay adjust input for ADC. Differential termination of $100\Omega$ inside the buffer.                                                                                  |

|                 | ADCDelAdjOut              | 50Ω differential output                                  | Stand-alone delay adjust output for ADC.                                                                                                                                            |

| Power Supplies  | GND                       | Ground 0V                                                | Common ground.                                                                                                                                                                      |

|                 | V <sub>EE</sub>           | Power -5V                                                | Digital negative power supply.                                                                                                                                                      |

|                 | V <sub>PlusDOut</sub>     | Adjustable power from 0V to +3.3V                        | Common mode adjustment of output buffers.                                                                                                                                           |

|                 | V <sub>CC</sub>           | Power +5V                                                | Digital positive power supply.                                                                                                                                                      |

TBGA 240 Package - Pinout

| Row    | Col      | Name                   | Row | Col | Name      | Row    | Col      | Name            | Row | Col      | Name           |

|--------|----------|------------------------|-----|-----|-----------|--------|----------|-----------------|-----|----------|----------------|

| Α      | 1        | NC                     | D   | 4   | VEE       | К      | 16       | VEE             | Т   | 17       | VEE            |

| Α      | 2        | E3                     | D   | 5   | VEE       | K      | 17       | GND             | Т   | 18       | ADCDELADJIN    |

| Α      | 3        | E5                     | D   | 6   | VPLUSDOUT | K      | 18       | I5B             | Т   | 19       | ADCDELADJINB   |

| Α      | 4        | E7                     | D   | 7   | VPLUSDOUT | K      | 19       | 15              | U   | 1        | F8             |

| Α      | 5        | E9                     | D   | 8   | VEE       | L      | 1        | H9              | U   | 2        | F9             |

| Α      | 6        | C0                     | D   | 9   | VPLUSDOUT | L      | 2        | RATIOSEL        | U   | 3        | VEE            |

| Α      | 7        | C2                     | D   | 10  | VEE       | L      | 3        | VPLUSDOUT       | U   | 4        | VPLUSDOUT      |

| Α      | 8        | C4                     | D   | 11  | VPLUSDOUT | L      | 4        | VPLUSDOUT       | U   | 5        | VPLUSDOUT      |

| Α      | 9        | C6                     | D   | 12  | VEE       | L      | 16       | VEE             | U   | 6        | VPLUSDOUT      |

| Α      | 10       | C8                     | D   | 13  | VPLUSDOUT | L      | 17       | VEE             | U   | 7        | VPLUSDOUT      |

| Α      | 11       | REFA                   | D   | 14  | GND       | L      | 18       | 16B             | U   | 8        | VEE            |

| Α      | 12       | A1                     | D   | 15  | VCC       | L      | 19       | 16              | U   | 9        | VPLUSDOUT      |

| Α      | 13       | A3                     | D   | 16  | VCC       | М      | 1        | H7              | U   | 10       | VEE            |

| Α      | 14       | A5                     | D   | 17  | GND       | М      | 2        | H8              | U   | 11       | VPLUSDOUT      |

| Α      | 15       | A7                     | D   | 18  | IOB       | М      | 3        | GND             | U   | 12       | VEE            |

| Α      | 16       | A9                     | D   | 19  | 10        | М      | 4        | GND             | Ū   | 13       | VPLUSDOUT      |

| Α      | 17       | DEMUXDELADJCTRL        | Е   | 1   | G6        | М      | 16       | GND             | U   | 14       | VPLUSDOUT      |

| Α      | 18       | RSTSYNCB               | E   | 2   | G7        | М      | 17       | GND             | Ü   | 15       | VPLUSDOUT      |

| Α      | 19       | NC                     | E   | 3   | VPLUSDOUT | М      | 18       | 17B             | Ü   | 16       | GND            |

| В      | 1        | E1                     | E   | 4   | VEE       | М      | 19       | 17              | Ü   | 17       | GND            |

| В      | 2        | E2                     | E   | 16  | VEE       | N      | 1        | <br>H5          | Ü   | 18       | GND            |

| В      | 3        | E4                     | Ē   | 17  | VEE       | N      | 2        | H6              | Ü   | 19       | GND            |

| В      | 4        | E6                     | E   | 18  | I1B       | N      | 3        | VPLUSDOUT       | V   | 1        | F7             |

| В      | 5        | E8                     | E   | 19  | 11        | N      | 4        | VPLUSDOUT       | V   | 2        | F6             |

| В      | 6        | REFC                   | F   | 1   | G4        | N      | 16       | VEE             | v   | 3        | F4             |

| В      | 7        | C1                     | F.  | 2   | G5        | N      | 17       | VEE             | V   | 4        | F2             |

| В      | 8        | C3                     | F.  | 3   | GND       | N      | 18       | I8B             | V   | 5        | F0             |

| В      | 9        | C5                     | F.  | 4   | GND       | N      | 19       | 18              | V   | 6        | D9             |

| В      | 10       | C7                     | F   | 16  | GND       | P      | 1        | H3              | V   | 7        | D7             |

| В      | 11       | C9                     | F   | 17  | GND       | P      | 2        | H4              | V   | 8        | D5             |

| В      | 12       | A0                     | F   | 18  | I2B       | P      | 3        | GND             | V   | 9        | D3             |

| В      | 13       | A2                     | F   | 19  | 12        | P      | 4        | GND             | V   | 10       | D1             |

| В      | 14       | A4                     | G   | 1   | G2        | P      | 16       | GND             | V   | 11       | REFD           |

| В      | 15       | A6                     | G   | 2   | G3        | P      | 17       | GND             | V   | 12       | B8             |

| В      |          |                        | G   | 3   | VEE       | P      |          | I9B             | V   | 13       | B6             |

|        | 16<br>17 | A8<br>ASYNCRESET       | G   | 4   | VEE       | P      | 18<br>19 | 196             | V   | 14       | В6<br>В4       |

| B<br>B |          |                        | G   | 16  | VEE       | R      |          |                 | V   |          | B2             |

| В      | 18       | DEMUXDELADJCTRLB       | G   | _   | VEE       |        | 1<br>2   | H1              | V   | 15       | B0             |

|        | 19       | RSTSYNC                | G   | 17  | I3B       | R<br>R | 3        | H2<br>VPLUSDOUT | V   | 16<br>17 | BIST           |

| С      | 1        | REFE                   |     | 18  |           |        | 4        |                 |     |          | _              |

| С      | 2        | E0                     | G   | 19  | 13        | R      |          | VPLUSDOUT       | V   | 18       | CLKINTYPE      |

| С      | 3        | VEE                    | Н   | 1   | G0<br>G1  | R<br>R | 16       | VEE             | V   | 19       | ADCDELADJCTRL  |

| С      | 4        | VPLUSDOUT<br>VPLUSDOUT | Н   | 2   | -         |        | 17       | GND             | W   | 1        | NC<br>FF       |

| С      | 5        |                        | Н   | 3   | GND       | R      | 18       | ADCDELADJOUT    | W   | 2        | F5             |

| С      | 6        | VPLUSDOUT              | Н   | 4   | GND       | R      | 19       | ADCDELADJOUTB   | W   | 3        | F3<br>F1       |

| С      | 7        | VPLUSDOUT              | Н   | 16  | GND       | T      | 1        | REFH            | W   | 4        |                |

| С      | 8        | VEE                    | Н   | 17  | GND       | T      | 2        | H0              | W   | 5        | REFF           |

| С      | 9        | VPLUSDOUT              | H   | 18  | CLKINB    | T      | 3        | VEE             | W   | 6        | D8             |

| С      | 10       | VEE                    | H   | 19  | CLKIN     | T      | 4        | VEE             | W   | 7        | D6             |

| С      | 11       | VPLUSDOUT              | J   | 1   | DR        | T      | 5        | VEE             | W   | 8        | D4             |

| С      | 12       | VEE                    | J   | 2   | REFG      | T      | 6        | VPLUSDOUT       | W   | 9        | D2             |

| С      | 13       | VPLUSDOUT              | J   | 3   | VPLUSDOUT | T      | 7        | VPLUSDOUT       | W   | 10       | D0             |

| С      | 14       | VPLUSDOUT              | J   | 4   | VCC       | T      | 8        | VEE             | W   | 11       | B9             |

| С      | 15       | VPLUSDOUT              | J   | 16  | VEE       | T      | 9        | VPLUSDOUT       | W   | 12       | B7             |

| С      | 16       | GND                    | J   | 17  | VEE       | T      | 10       | VEE             | W   | 13       | B5             |

| С      | 17       | GND                    | J   | 18  | I4B       | T      | 11       | VPLUSDOUT       | W   | 14       | B3             |

| С      | 18       | GND                    | J   | 19  | 14        | T      | 12       | VEE             | W   | 15       | B1             |

| С      | 19       | DIODE                  | K   | 1   | SWIADJ    | Т      | 13       | VPLUSDOUT       | W   | 16       | REFB           |

| D      | 1        | G8                     | K   | 2   | DRB       | Т      | 14       | VPLUSDOUT       | W   | 17       | NBBIT          |

| D      | 2        | G9                     | K   | 3   | VEE       | Т      | 15       | GND             | W   | 18       | ADCDELADJCTRLB |

| D      | 3        | VEE                    | K   | 4   | VEE       | Т      | 16       | VEE             | W   | 19       | NC             |

Figure 20. TBGA 240 Package: Bottom View

| 19                  | 18                 | 17               | 16   | 15            | 14       | 13       | 12            | 11         | 10       | 9        | 8             | 7         | 6          | 5             | 4          | 3          | 2          | 1          |   |

|---------------------|--------------------|------------------|------|---------------|----------|----------|---------------|------------|----------|----------|---------------|-----------|------------|---------------|------------|------------|------------|------------|---|

|                     | RstSyncb I         | Denluxdeladjetro | A9   | (A7)          | (A5)     | (A3)     | (A1)          | REFA       | (C8)     | (C6)     | (C4)          | (C2)      | (CO)       | (E9)          | (E7)       | <b>E</b> 5 | (E3)       |            | А |

| RstSync             | Demuxdeladjotrcl   | b (syncrese)t    | (A8) | (A6)          | (A4)     | (A2)     | (A0)          | (C9)       | (C7)     | (C5)     | (C3)          | (C1)      | REFO       | (E8)          | <b>E</b> 6 | E4         | (E2)       | E1         | В |

| DIODE               | GND                | GND              | GND  | (VPLUSD)      | (VPLUSD) | VPLUSD   | VEE           | VPLUSD     | VEE      | VPLUSD   | VEE           | (VPLUSD)  | (VPLUSD)   | (PLUSD)       | VPLUSD     | VEE        | E0         | REFE       | С |

| 10                  | (l0b)              | GND              | VCC  | VCC           | GND      | (PLUSD)  | VEE           | VPLUSD     | VEE      | (VPLUSD) | VEE           | (PLUSD)   | (VPLUSD)   | VEE           | VEE        | VEE        | <b>G</b> 9 | <b>G8</b>  | D |

| (I1)                | (I1b)              | VEE              | VEE  | $\langle$     |          | X        | $\overline{}$ |            | X        |          | <del></del>   | X         | /          | $\supset$     | VEE        | (VPLUSD)   | <b>G</b> 7 | <b>G</b> 6 | E |

| (12)                | (l2b)              | GND              | GND  |               | $\times$ |          | $\times$      | $\times$   | / \      | $\times$ | $\rightarrow$ |           | X          |               | GND        | GND        | <b>G</b> 5 | G4         | F |

| (3)                 | (I3b)              | VEE              | VEE  | $\rangle$     | /        | $\times$ |               |            | $\times$ |          |               | $\times$  | / \<br>\ / | X             | VEE        | VEE        | <b>G</b> 3 | G2         | G |

| CLK                 | CLKb               | GND              | GND  | $\searrow$    |          | \/       | $\times$      | $\nearrow$ | \/       | X        | $\nearrow$    |           | X          |               | GND        | (GND)      | G1)        | G0         | Н |

| [4]                 | (I4b)              | VEE              | VEE  |               | $\times$ |          | $\times$      | $\times$   |          | $\times$ | $\overline{}$ |           | $\times$   |               | VCC        | VPLUSD     | REFG       | DR         | J |

| (15)                | (I5b)              | GND              | VEE  | $\rightarrow$ | /<br>\   | $\times$ |               |            | $\times$ | ′\<br>\/ | $\times$      | $\times$  | / \<br>\ / | X             | VEE        | VEE        | DRb        | SWladj     | К |

| (l6)                | (l6b)              | VEE              | VEE  |               | X        | <u> </u> | X             | $\nearrow$ |          | X        | $\nearrow$    |           | X          |               | (PLUSD)    | VPLUSD     | RATIOSE.   | (H9)       | L |

| [7]                 | (I7b)              | GND              | GND  |               | $\times$ |          | $\times$      | $\searrow$ |          | $\times$ | $\searrow$    |           | $\times$   |               | GND        | GND        | (H8)       | H7         | М |

| (18)                | (I8b)              | VEE              | VEE  | $\rightarrow$ |          | $\times$ |               |            | $\times$ |          | $\times$      | $\times$  | / \        |               | VPLUSD     | (VPLUSD)   | (H6)       | (H5)       | N |

| [9]                 | [9b]               | GND              | GND  |               | $\times$ |          | $\times$      | $\times$   | ,<br>\_/ | X        | $\nearrow$    |           | $\times$   |               | GND        | GND        | H4         | (H3)       | Р |

| ADC (telayadjo) utl | B All Cdelayadjou  | t (GND)          | VEE  | $\vee$        |          | X        |               |            | $\Delta$ |          | <u> </u>      |           |            | <i>&gt;</i> ) | (VPLUSD)   | VPLUSD     | H2         | (H1)       | R |

| AD (delayad) nE     | B All Cdelayarijin | VEE              | VEE  | GND           | (VPLUSD) | (VPLUSD) | VEE           | (VPLUSD)   | VEE      | (PLUSD)  | VEE           | VPLUSD    | (VPLUSD)   | VEE           | VEE        | VEE        | (H0)       | REFH       | Т |

| GND                 | (GND)              | GND              | GND  | (VPLUSD)      | (VPLUSD) | (VPLUSD) | VEE           | (VPLUSD)   | VEE      | VPLUSD   | VEE           | (PLUSD)   | (VPLUSD)   | (VPLUSD)      | (VPLUSD)   | VEE        | (F9)       | F8         | U |

| ADCIDELADJC TF      | RL OLKINTYPE       | BIST             | (B0) | B2            | (B4)     | (B6)     | (B8)          | REFD       | (D1)     | D3       | (D5)          | (D7)      | D9         | (F0)          | (F2)       | (F4)       | (F6)       | (F7)       | V |

| L OA                | DCDELADJC RL       | b (NbBIT)        | REFB | B1            | B3       | B5       | (B7)          | B9         | (D0)     | (D2)     | D4            | <u>D6</u> | D8         | REFF          | (F1)       | (F3)       | (F5)       |            | w |

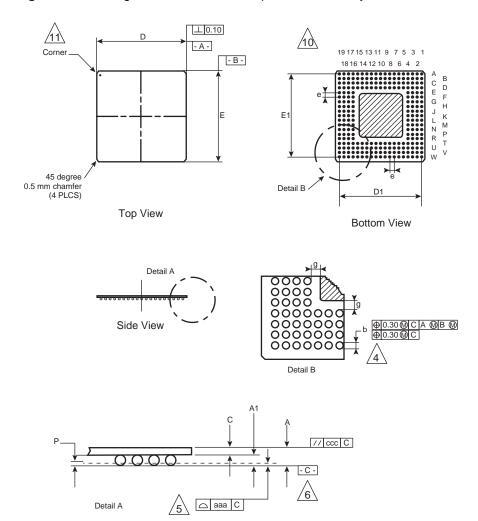

# Outline Dimensions

Figure 21. Package Dimension – 240 Tape Ball Grid Array

| Dimensional References |                 |              |       |  |  |  |  |  |

|------------------------|-----------------|--------------|-------|--|--|--|--|--|

| Ref.                   | Min.            | Nom.         | Max.  |  |  |  |  |  |

| Α                      | 1.30            | 1.50         | 1.70  |  |  |  |  |  |

| A1                     | 0.50            | 0.60         | 0.70  |  |  |  |  |  |

| D                      | 24.80           | 25.00        | 25.20 |  |  |  |  |  |

| D1                     |                 | 22.86 (BSC.) |       |  |  |  |  |  |

| E                      | 24.80           | 25.00        | 25.20 |  |  |  |  |  |

| E1                     | E1 22.86 (BSC.) |              |       |  |  |  |  |  |

| b                      | 0.60            | 0.75         | 0.90  |  |  |  |  |  |

| С                      | c 0.80          |              | 1.00  |  |  |  |  |  |

| M                      | 19.00           |              |       |  |  |  |  |  |

| N                      | 240.00          |              |       |  |  |  |  |  |

| aaa                    | -               | -            | 0.15  |  |  |  |  |  |

| ccc                    | -               | -            | 0.25  |  |  |  |  |  |

| е                      | 1.27 TYP.       |              |       |  |  |  |  |  |

| g                      | 0.35            | -            | -     |  |  |  |  |  |

| Р                      | 0.15            | 0.15         |       |  |  |  |  |  |

Notes: 1. All dimensions are in millimeters.

- 2. "e" represents the basic solder ball grid pitch.

- "M" represents the basic solder ball matrix size, and symbol "N" is the maximum allowable number of balls after depopulating.

- b" is measured at the maximum solder ball diameter parallel to primary datum C -

- 5 Dimension "aaa" is measured parallel to primary datum C -

- Primary datum -C- and seatin plane are defined by the spherical crowns of the solder balls.

- 7. Package surface shall be black oxide.

- 8. Cavity depth various with die thickness.

- 9. Substrate material base is copper.

- Bilateral tolerance zone is applied to each side of package body.

- 45 deg. 0.5 mm chamfer corner and white dot for pin 1 identification.

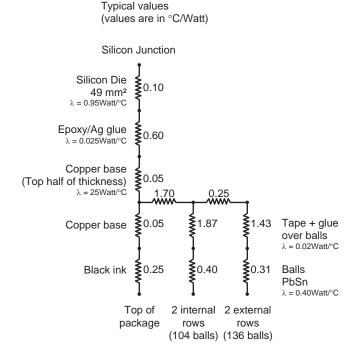

# Thermal and Moisture Characteristics

Thermal Resistance from Junction to Case: RTHJC

The Rth from junction to case for the TBGA package is estimated at 1.05°C/W that can be broken down as follows:

- Silicon: 0.1°C/W

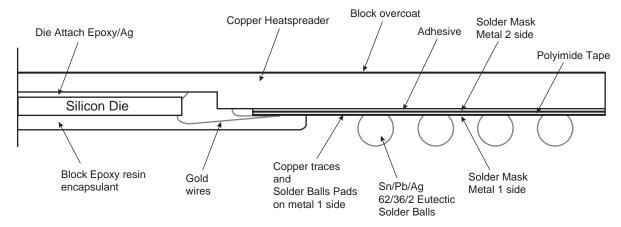

- Die attach epoxy: 0.5°C/W (thickness # 50 μm)

- Copper block (back side of the package): 0.1°C/W

- Black Ink: 0.251°C/W.

# Thermal Resistance from Junction to Ambient: RTHJA

A pin-fin type heat sink of a size 40 mm x 40 mm x 8 mm can be used to reduce thermal resistance. This heat sink should not be glued to the top of the package as Atmel cannot guarantee the attachment to the board in such a configuration. The heat sink could be clipped or screwed on the board.

With such a heat sink, the Rthj-a is about 6°C/W (if we take 10°C/W for Rth from the junction to air through the package and heat sink in parallel with 15°C/W from the junction to the board through the package body, through balls and through board copper).

Without the heat sink, the Rth junction to air for a package reported on-board can be estimated at 13 to 20°C/W (depending on the board used).

The worst value 20°C/W is given for a 1-layer board (13°C for a 4-layer board).

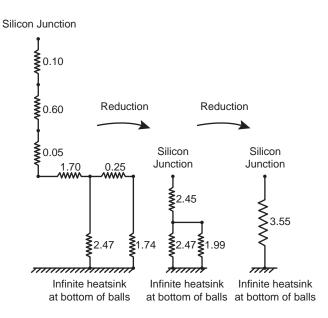

# Thermal Resistance from Junction to Bottom of Balls

The thermal resistance from the junction to the bottom of the balls of the package corresponds to the total thermal resistance to be considered from the silicon's die junction to the interface with a board. This thermal resistance is estimated to be 4.8°C/W max.

The following diagram points out how the previous thermal resistances were calculated for this packaged device.

Figure 22. Thermal Resistance from Junction to Bottom of Balls

DEMUX - Axpproximative Model for 240 TBGA

Assumptions:

Square die 7.0 x 7.0 = 49 mm², 75  $\mu$ m thick Epoxy/Ag glue, 0.40 mm copper thickness under die, Sn60Pb40 columns diameter 0.76 mm, 23 x 23 mm TBGA

Thermal Resistance Junction to case typical = 0.10 + 0.60 + 0.05 + 0.05 + 0.25 = 1.05°C/W

Thermal Resistance Junction to case Max = 1.40°C/W

Case were all Bottom of Balls are connected to infinite heatsink (values are in °C/Watt)

Thermal Resistance Junction to bottom of balls = 4.8°C/W Max

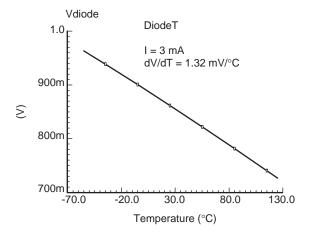

## Temperature Diode Characteristic

The theoretical characteristic of the diode according to the temperature when I = 3 mA is depicted below.

Figure 23. Temperature Diode Characteristic

### Moisture Characteristic

This device is sensitive to moisture (MSL3 according to the JEDEC standard).

The shelf life in a sealed bag is 12 months at < 40°C and < 90% relative humidity (RH).

After this bag is opened, devices that might be subjected to infrared reflow, vapor-phase reflow, or equivalent processing (peak package body temperature 220°C) must be:

- mounted within 168 hours at factory conditions of ≤ 30°C/60% RH, or

- stored at ≤ 20% RH.

The devices require baking before mounting, if the humidity indicator is > 20% when read at  $23^{\circ}\text{C} \pm 5^{\circ}\text{C}$ .

If baking is required, the devices may be baked for:

- 192 hours at 40°C + 5°C/-0°C and < 5% RH for low temperature device containers, or

- 24 hours at 125°C ± 5°C for high-temperature device containers.

### Detailled Cross Section

The following diagram depicts a detailed cross section of the DMUX TBGA package.

Figure 24. TBGA 240: 1/2 Cross Section

In the DMUX package shown above, the die's rear side is attached to the copper heat spreader, so the copper heat spreader is at -5V.

It is necessary to use a heat sink tied to the copper heat speader.

Moreover, there is only a little layer of painting over the copper heat spreader which does not isolate it.

It is therefore recommended to either isolate the heat sink from the other components of the board or to electrically isolate the copper heat spreader from the heat sink. In the latter case, one should use adequate low Rth electrical isolation.

# Applying the TS81102G0 DMUX

The TSEV81102G0 DMUX evaluation board is designed to be connected with the TSEV8388G and TSEV83102G0 ADC evaluation boards.

Figure 25. TSEV81102G0 DMUX Evaluation Boards

Please refer to the "ADC and DMUX Application Note" for more information.

# ADC to DMUX Connections

The DMUX inputs configuration has been optimized to be connected to the TS8388B ADC.

The die in the TBGA package is up. For the ADC, different types of packages can be used such as CBGA with die up or the CQFP68 down. The DMUX device being completely symmetrical, both ADC packages can be connected to the TBGA package of the DMUX crisscrossing the lines (see Table 8).

Table 8. ADC to DMUX Connections

| ADC Digital Outputs<br>CQFP68 Package |                  |    | DMUX Data Inputs<br>TBGA Package |  |  |

|---------------------------------------|------------------|----|----------------------------------|--|--|

| D0                                    | 17               | D0 | 10                               |  |  |

| D1                                    | 16               | D1 | I1                               |  |  |

| D2                                    | 15               | D2 | 12                               |  |  |